The search for a processor - MPW and chipIgnite - page 2

-x-x-x-

Hammer VLSI flow - supported in Chipyard

https://docs.fires.im/en/stable/index.html

latest workshop (march 2023):

TODO: watch all of them

https://fires.im/workshop-2023/

- videos on a wide array of topics

https://fires.im/asplos-2023-tutorial/

Chipyard

https://www.youtube.com/watch?v=EXbs5VSv19c

- chipyard basics

https://www.youtube.com/watch?v=VOcSpfM7KXk

TileLink Uncached Lightweight (TL-UL)

- which adds various hints, atomic operations, and burst accesses but without support for coherent caches.

Finally, TileLink Cached (TL-C)

- is the complete protocol, which supports use of coherent caches.

- https://doc-en.rvspace.org/JH7100/Datasheet/JH7100_DS/chiplink.html

- scifive proprietery implementation of the tile link protocol for off-chip application:

https://forums.sifive.com/t/chiplink-isnt-an-open-spec-apparently-or-can-i-see-it-somewhere/1479/2

- tile link implementation over networking protocol - ethernet if I am not wrong

- can share cache coherent memory across a long graph - even with offchip memory

https://www.youtube.com/watch?v=5Ax-qxK3fxE

- motivation: datacenter + AI / ML accelerators with cache coherent memory

Demo with Xilinx

https://www.youtube.com/watch?v=hmVNTUrJoDM

here capability discovery would be an issue when hot-wiring chips / components / actors / nodes

Cache Coherence

- snooping and directory based protocols introduction

https://www.youtube.com/watch?v=YNpaELJZm2c

- Snooping based protocols details

-x-x-x-x-

although his hello !! is a bit over the top, the animations and explanations are on point.

Debugging with OpenLane and OpenRoad

####### Monday 03 July 2023 08:23:51 PM IST #######

Wishbone bus demo with the Caravel base wrapper

- similar exercise in text

https://av.tib.eu/media/40048

- good framework for auto discovery

Building riscduino

git clone git@github.com:sanyamsmulay/riscduino.git

cd riscduino

git submodule init

git submodule update make setup

--> should build everything

-x-x-x-

- this did not work out of the box.. needs fixing - (it has become out of date)

- openlane make step for sky130-pdk failing

- trying to find a version of openlane where the make for the sky130-pdk is running

- currently conda.cli was not found

- pointing the openlane to tag:2023.03.08

git@github.com:sanyamsmulay/riscduino.git

error:

iverilog sorry: constant selects in always_* processes are not currently supported

(all bits will be included)

- tried all the generation flags available - the error does not change

- assuming a fresh build of iverilog would be able to run this

- built iverilog from source

- iverilog - local build needs glibc --> 2.34

iverilog/bin/iveriloglocal_install: /lib/x86_64-linux-gnu/libc.so.6: version `GLIBC_2.34' not found

https://superuser.com/a/537694 --> talks about the above errorhttps://superuser.com/questions/537683/how-to-fix-lib-x86-64-linux-gnu-libc-so-6-version-glibc-2-14-not-found --> other interesting solutions on the thread

guide: https://www.linuxfromscratch.org/lfs/view/11.0/chapter08/glibc.html

code: https://www.linuxfromscratch.org/lfs/view/11.0/chapter03/packages.html

pre-built: (https://launchpad.net/ubuntu/+source/glibc/2.34-0ubuntu2)

will try this next if the build from source does not work

- asm needs to have correct header files

https://stackoverflow.com/a/26473181 (idea for symbolic link from this post)

hint: search dpkg for the header file prctl.h and link the appropriate one

- was already installed: linux-libc-devso that artefacts from the failed steps do not affect the build

95.

Riscduino

https://github.com/dineshannayya/riscduino

- wishbone bus

repo: https://github.com/dineshannayya/riscduino

- documentation is great

intro video by the maintainer: https://www.youtube.com/watch?v=lFVnicPhTI0

arduino IDE / sketch definitions for connecting to and programming the PCB

https://github.com/dineshannayya/riscduino_board

https://theopenroadproject.org/implementation-of-riscduino-core-using-a-hierarchical-design-flow/

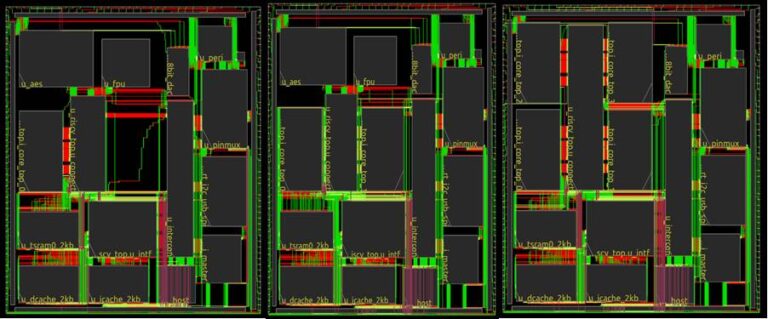

- build using openROAD and OpenLane

- uses hierarchical design

group similar blocks - fragmented floorplan makes top-level timing closure difficult

logically partitioning the blocks - makes faster RTL-GDSII runtime and timing clusure easy

manual macro pin placement - gives better global routing (one way of saying the project id not good enough to auto route :P)

OpenROAD can give a preview for macro-connectivity, Eg:

run timing at top-level first,

if with the above thumb-rule, there are violations at the top, make room in the macro/lower level constraints, make sure the macro is not violating the lower margins and run again for top level.

Flow Summary

- 150K cells + 48 Kb SRAM (from sky130 pdk)

- fmax of 100Mhz.

efabless: components marketplace for ASIC design:

https://platform.efabless.com/design_catalog/info

### Wednesday 08 February 2023 11:23:23 PM IST #######

How to build for the MPW-6 (should be similar for other shuttles I think)

https://www.youtube.com/watch?v=MNuoYz_MM-c

####### Wednesday 08 February 2023 11:18:29 PM IST #######

98.

The next Open MPW shuttle ?

- not getting any info

###### Wednesday 08 February 2023 11:08:45 PM IST #######

99.

riscduino - is based on the caravel base chip template

https://github.com/dineshannayya/riscduino

more about it on #95.

####### Wednesday 08 February 2023 10:57:53 PM IST #######

100.

https://www.youtube.com/watch?v=vJqP7ZR0NrI

Open MPW

- google sponsored shuttle

chipIgnite

- 9725 USD

- for:

-- 300 WCSP OR -- 100 QFN -

-- 5 evaluation boards

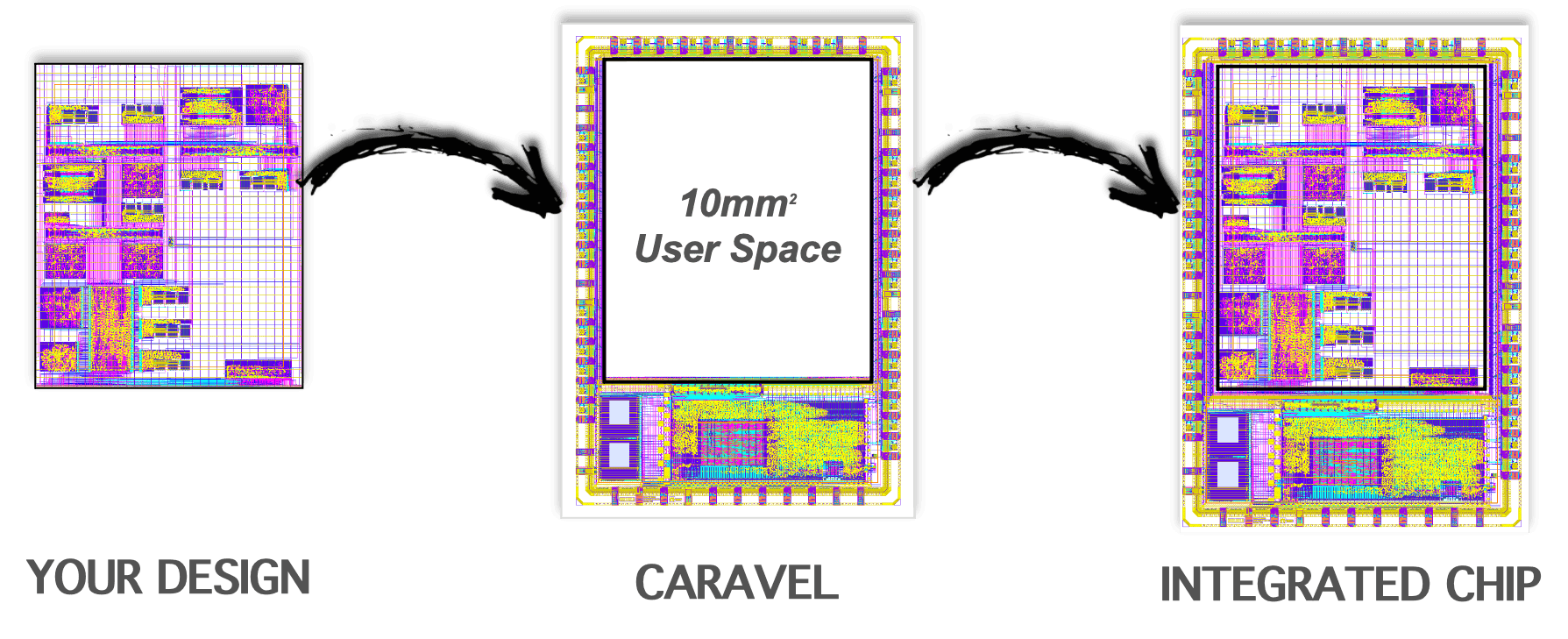

caravel base chip

- https://github.com/efabless/caravel

- management area + user project area

- 10mm sq user area

- management area - good base functionality (very tightly packed ! )

- some genius features of the management SoC

-- access to SPI of the user area SPI as slave - can be used for configuring at runtime (eg. the guitar string project)

-- access to user area wishbone as master (can check if rest of the chip is working well or not )

-- protection from user area on the wishbone bus

-NOICE !

this a good starter for a chip in-itself.

Steps for building for an open mpw shuttle

- Integrate design into the caravel user wrapper

- verify the HDL integration

- Harden Design

- submission pre-check

- submit for tapeout

Comments

Post a Comment